# Scalability and Predictability Model of PLC Systems

# **Max Fornander**

Division of Industrial Electrical Engineering and Automation Faculty of Engineering, Lund University

# Lund University

# Faculty of Engineering

Division of Industrial Electrical Engineering and Automation

# Scalability and Predictability Model of PLC Systems

Academic supervisor:

Ulf Jeppsson Industrial supervisors: Ulf Thomsen Plym Peter Stoltenberg Examiner: Gunnar Lindstedt

> Thesis written by: Max Fornander

October 2024

#### Abstract

This master's thesis is commissioned by SAAB Group with the purpose of developing a model which can be used to estimate the margin for expansion of devices in PLC systems. Although commercial PLC systems are hard real-time systems, they have inherited unpredictable characteristics due to off-the-shelves components. This makes it difficult to measure the impact on performance when a new device is connected to the system.

By pressuring the CPU using a computationally heavy control program, the scheduler is forced to prioritize tasks associated with the addition of a device. This may increase the accuracy of measuring the impact of an increasing number of devices on CPU performance. The commercial PLC system and all devices used are manufactured by B&R, a member of ABB group providing solutions within industrial automation.

The method consists of measuring idle and cyclic CPU usage (%) before and after a device is connected to the system. This is done using Profiler, a profiling tool provided by B&R. The resulting models, using linear approximation and ridge regression, is capable of predicting the impact on idle and cyclic CPU usage (%) when adding a device to a test setup of similar size to previously measured systems. Although the gathered quantity of data samples can be considered low, the predictions regarding idle load (%) was accurate.

Furthermore, the industrial Ethernet protocol (Powerlink) used in the B&R system is evaluated. Specifically to detect circumstances which might impact the CPU load and the number of devices existing within a single network. Program optimization is briefly investigated and two programming conventions are identified as important for maintaining a large number of devices.

#### Sammanfattning

Detta examensarbete är gjort i samarbete med Saab Group med syftet att utveckla en modell för att estimera den marginal som finns gällande antalet enheter i ett PLC system. Även om kommersiella PLC system är hårda realtidssystem, så innehar de till viss del fortfarande opredikterbara beteenden. Detta medför en viss svårighet med att mäta inverkan på systemets prestanda när en ny enhet kopplas in i systemet.

Genom att öka arbetslasten på processorn med hjälp av ett beräkningsmässigt krävande kontrollprogram, så tvingas systemet att prioritera dess resurser kopplade till den nya enheten. Hypotesen är att detta leder till en förbättrad mätmetod, som ger ett tydligare resultat för hur mycket en enhet faktiskt påverkar processorlasten. PLC systemet och all kringutrustning som använts tillverkas av företaget B&R, som ingår i ABB-koncernen och är specialiserat på lösningar inom industriell automation.

Metoden mäter skillnaden i tomgång och cyklisk last (%) före och efter att en ny enhet kopplas in i systemet. Processorlast mäts med Profiler, ett profileringsverktyg som tillhandahålls av B&R. Med hjälp av resultatet utvecklas två modeller, varav ena baseras på linjär approximering och andra ridge regression. Modellerna predikterar påverkan på processorlasten då nya enheter kopplas in i testsystem av liknande storlek, trots en låg mängd insamlade mätvärden. Specifikt sågs goda prediktioner gällande tomgångslasten.

Därefter undersöks det industriella kommunikationsprotokoll som finns i PLC-systemet. Dels för att hitta eventuella begränsningar gällande antalet inkopplade enheter, dels för att se hur processorn påverkas av större nätverk. Till sist undersöks kodningskonventioner som kan förbättra prestandan för system med många enheter.

#### Acknowledgements

Jag vill börja med att tacka Joakim på Saab som gav mig möjligheten att genomföra detta examensarbete. Det har varit mycket utvecklande att själv få forma arbetet och hitta egna svar, samt få en inblick i hur en bra arbetsplats med god stämning och glada kollegor ska se ut!

Ett väldigt stort tack till både Ulf och Peter på Saab som hjälpt mig att komma igång och ro arbetet i hamn. Med stort tålamod och pedagogisk förmåga har de besvarat alla frågeställningar under arbetets gång och samtidigt bidragit till att man känt sig välkommen på företaget. Stort tack!

Till handledare Ulf och examinator Gunnar på LTH vill jag även rikta min stora tacksamhet. Trots sina fulla agendor har de bidragit med sin tid, kunskap och känsla för akademiska detaljer.

Sist men inte minst vill jag tacka min familj (som under arbetets gång utökats med en fantastisk liten individ) för deras tålamod, stöd och hejarop!

# Contents

| Ι            | In      | troduction                                        | 1        |

|--------------|---------|---------------------------------------------------|----------|

|              | I.I     | Background                                        | 1        |

|              | I.II    | Objectives                                        | 2        |

|              | I.III   | Limitations                                       | 2        |

| п            | Lit     | terature review                                   | 3        |

|              | II.I    | General information regarding PLC systems         | 3        |

|              | II.II   | B&R's system                                      | 4        |

|              | II.III  | Academic foundation                               | 4        |

| II           | I Th    | leory                                             | <b>5</b> |

|              | III.I   | The scan cycle                                    | 5        |

|              | III.II  | The real-time operating system                    | 6        |

|              | III.III | Hardware                                          | 8        |

|              | III.IV  | Limitations in network capacity                   | 8        |

|              | III.V   | Program optimization                              | 9        |

|              | III.VI  | Developing a scalability and predictability model | 9        |

| IV           | n M     | ethod                                             | 11       |

|              | IV.I    | Equipment and setup                               | 11       |

|              | IV.II   | Node and I/O testing                              | 12       |

|              |         | Network                                           | 14       |

|              | IV.IV   | Program optimization                              | 15       |

| $\mathbf{v}$ | Re      | esults                                            | 18       |

|              | V.I     | Node and I/O testing                              | 18       |

|              | V.II    | Network                                           | 24       |

|              | V.III   | Program optimization                              | 25       |

| $\mathbf{V}$ | [ Di    | scussion                                          | 33       |

|              | VI.I    | General                                           | 33       |

|              | VI.II   | Future work                                       | 37       |

|              | VI.III  | Difficulties                                      | 38       |

| $\mathbf{V}$ | II Co   | onclusions                                        | 39       |

### Terminology

A list of terms and abbreviations used in the thesis.

#### Terms

- **Channel** Each module has a varying number of channels through which digital or analog signals can be received or sent.

- **Device** Refers to both modules, nodes, or any other component connected to the PLC directly or indirectly, which could potentially impact performance.

- Module A single I/O component attached directly either to a node or serially to the PLC itself.

- Node A connection point within the network onto which modules are attached.

- **Powerlink** An industrial Internet protocol.

- Task A set of instructions executed by the CPU.

- Wireshark Tool used to observe/capture network communication.

#### Acronyms

- ARP Adress resolution protocol, an internet communication protocol.

- API Application programming interface, offers services between software applications.

- CPU Central Processing Unit, as in computer hardware.

- FB Function block, used in PLC programming.

- FBD Function block diagram, used in PLC programming.

- FC Function, used in PLC programming.

- IEC International Electrotechnical Commission, an international standards organization.

- IL Instruction list, used in PLC programming.

- ISR Interrupt service routine, part of operating system.

- I/O Input or output.

- I/O Pair One input module cross-coupled to an output module.

- LD Ladder diagram, used in PLC programming.

- LLDP Link-layer discovery protocol, internet communication protocol.

- **PLC** Programmable Logic Controller.

- PLK Powerlink, B&R's industrial communication protocol.

- PMU Performance Measurement Unit, part of Intel's processors.

- POU Program organization unit, used in PLC programming.

- **PRG** Program,, used in PLC programming.

- **RAM** Random Access Memory, as in computer hardware.

- **RTOS** Real-Time Operating System.

- SFC Sequential Function Chart, used in PLC programming.

- **ST** Structured text, used in PLC programming.

- TCB Task Control Block, contains task related information.

- UDP User Datagram Protocol, an Internet protocol.

- **UDT** User Defined Data Type, used in PLC programming.

# I Introduction

This chapter serves as a brief overview of the thesis by first introducing PLC systems and providing the reader with the necessary background information to delve into the problem statement. The final section describes the objectives and limitations regarding developing a model for scalability and predictability.

#### I.I Background

A Programmable Logic Controller (PLC) sets itself apart from other types of controllers used in industrial automation by prioritizing robustness and real-time signal processing. Set in context, the PLC reads inputs such as signals from sensors, processes these values according to a user defined control program, and finally updates outputs such as signals to actuators. The described sequence of operations, known as the scan cycle, occurs periodically with a fixed periodicity.

The PLC is referred to as a hard real-time system, meaning any time exceeding the scan cycle period results in system failure. This makes the PLC ideal for controlling processes where timing and reliability is vital. Every hardware component in the PLC is chosen to mitigate any risk of delays and to decrease response time while also ensuring operating for extended periods of time in harsh industrial environments. The downside with this feature is the resulting limitations on, e.g., number of CPU cores, or memory size, which decreases the PLCs computational capabilities.

Today, most PLC systems are modular, meaning they can be expanded with additional devices which enhance the system's capabilities such as *modules* for increased I/O functionality. Modules can in turn be attached to the system through devices known as *nodes*. A PLC system's ability to expand the number of connected devices while maintaining system performance is referred to as its *scalability*. A system's scalability could theoretically be measured by evaluating how much a device impacts system performance indicators such as CPU usage (%).

Adding a device affects multiple layers of the system, such as activating additional tasks, introducing delays through sampling of signals and then sending/receiving data through a network of nodes. A system's *predictability* refers to how consistently and reliably the system behaves in response to changes. Every PLC type reacts differently to the addition of a device, the performance might either gradually or suddenly change. This project investigates whether it is possible to develop a model describing a PLC system's scalability and predictability. The intended use of the model is to predict a margin for how much more the system can be expanded with additional devices. The thesis is commissioned by SAAB Group who provides solutions within military defence and civil security.

Research in this field presents several challenges. To begin with, the thesis focuses on commercially available systems. Those often use proprietary hardware and software solutions, resulting in limited transparency regarding their design and performance. Only studies tied to the evaluation of real-time systems in general was found through the literature study. In the rare case that the performance of PLC systems was evaluated, it was solely related to novelty hardware architectures, and not commercial systems.

The chosen work method to evaluate the impact on performance by a single device is to measure CPU usage (%) before and after a new device is connected. All while a computationally heavy control program is executed on the PLC to further isolate the impact of said device. Differences between analog and digital modules will first be investigated. Followed by different configurations of nodes and modules. Since there exist numerous node and module configurations, two different cases will be investigated. At first using a "balanced" setup, with an equal number of modules per node, followed by an "unbalanced" setup, with a different number of modules per node.

Another aspect regarding scalability and predictability is the impact on the network from adding a device. This is investigated by simulating heavy data traffic using packet flooding, while monitoring CPU usage (%) and irregularities in both the Ethernet and industrial Ethernet protocol network. Finally, PLC performance is tied to the optimization level of the program code. Since program optimization regarding PLC systems is a vast research field, only very basic aspects regarding code optimization for maintaining an expanding system will be investigated.

#### I.II Objectives

The thesis was commissioned by submarine manufacturer SAAB Kockums, part of SAAB Group. Needless to say, storage is a scarce commodity onboard submarines. This is why great care has to be taken into planning the PLC system and any potential future upgrades. Hence, SAAB Kockums seeks to develop a model which predicts the performance of a PLC system with certain numbers (and types) of connected devices. The model should provide a marginal for the number of devices that can be connected in the future. The model should help in identifying factors in the system which inhibit scalability and predictability. The thesis will at the end give an answer to the following problem statement: Is it possible to create an applicable model for scalability and predictability for a commercially available PLC system?

The following objectives were defined at the start of the project regarding developing a model for scalability and predictability:

- Establish the relationship between impact on system performance and the number/type of device(s) for a commercially available PLC system.

- Investigate limitations surrounding the network regarding number of devices.

- Investigate programming conventions which could increase the number of devices.

#### I.III Limitations

The PLC and all its components (nodes and modules) used for testing is built by the manufacturer B&R. This limits general application of the model since there are many design differences in hardware and software between manufacturers, and even within product line-ups themselves. To mitigate the risk of the thesis turning into an evaluation of B&R's systems, the chosen measurements (idle and cyclic CPU usage (%)) can be measured using common profiling tools, further improving the usability of the chosen method and model.

The thesis was written by one engineering student with the aid of both industrial supervisors at SAAB Group and academic supervisors at LTH. The time frame for the thesis spanned from October 2023 to June 2024. During the period quite some time was spent familiarizing with both the PLC hardware and accompanying software suite. Furthermore, some time was set aside for security clearance to visit the offices holding the testing equipment.

Another hindrance was the lack of academic studies found during the literature study related to scalability and/or predictability models of PLC systems. As such, additional time was spent devising both a working methodology for reliably gathering useful measurements, and finally an applicable model. As previously mentioned, there are also generally limited information regarding commercial systems since manufacturers rarely disclose performance numbers.

# II Literature review

This chapter contains general information regarding PLC systems as well as information regarding academic foundation.

#### **II.I** General information regarding PLC systems

The programmable logic controller was first invented by two competing companies, Allen Bradley and Bedford Associates, who both responded to General Motors wishes to replace mechanical relay sequencing used in the automobile industry [1]. While the mechanical relays provided real-time communication capabilities, they did not allow for quick changes to the internal logic. Any mistakes made along the development of the circuitry resulted in increased development costs and production delays. During the 1960's the computer was very fragile and required dust-free environments, opposite of the conditions in which the mechanical relays were operating. Furthermore, the early computers were large, slow, and expensive [1].

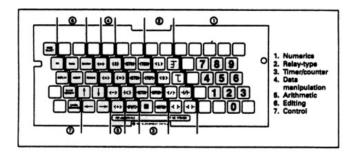

Thus, a new type of computer had to be developed. The computer used in the industrial setting had to be robust. It should handle sudden power supply changes, behave predictably during abrupt interrupts, and withstand environmental complications such as temperature or signal interference due to radiation. The computer would also be remained untouched for long periods of time after installation, putting high priority on predictability [1]. The new computer should also be easily programmed by the same workers who developed the sequential relays. Hence, the resulting computer had a very different keyboard-layout compared to today, see Figure 1.

Figure 1: The PLC developed by Allen-Bradley used the same symbols as in conventional sequential relays.

The modern PLC system has stood the test of time because it fills a very specific role. Today, there are more than twenty global manufacturers of PLC systems, each with their own design, software suite, and specialized applications [2]. A comparison between the modern [3] and early [4] Allen-Bradley PLC system shows that the very first PLCs had designs similar to those of today, see Figure 2-3. However, the functionality of PLCs has drastically evolved since the 1960's. While PLCs initially emerged in the automobile industry, they are now used across nearly all sectors of society, e.g., energy, healthcare, and infrastructure.

Figure 2: Allen-Bradley's CompactLogix 5380, launched in 2016.

Figure 3: Allen-Bradley's first commercial PLC, the PDQ-II, launched in 1969.

#### II.II B&R's system

The system used in this thesis is manufactured by B&R, a member of the ABB-group specializing in solutions within industrial automation such as safety PLC's for processing lines or machines automated with B&R controllers [5]. The PLC unit used is the CP3586 (see Figure 4) containing an Intel Atom clocked at 1.6 MHz. Modules can be connected directly to the PLC using a X2X-link connection, or through nodes using B&R's proprietary industrial communication protocol known as Powerlink.

Figure 4: The PLC used in this project; the CP3586, manufactured by B&R. Here with additional modules attached serially using the X2X-link connection.

#### **II.III** Academic foundation

Studies found regarding performance of commercially available PLCs in general are scarce. While some studies are found in which an attempt at standardizing benchmarks between manufacturers where found (e.g., [6]), these types of studies does not focus on translating the measured CPU performance into an applicable number of devices. Other studies focused on hardware architectures (e.g., [7]), which evaluate the impact on scan cycle performance in PLC systems from using multicore CPUs. However, little is said about how these improvements can affect scalability. Instead, the literature review focused on aspects within hardware (e.g., [8]) and software (e.g., [9]) which generally impacts the performance of hard real-time systems, not always specifically PLCs.

### III Theory

Here technical aspects related to PLC systems, model development, program optimization, and network evaluation are discussed.

#### III.I The scan cycle

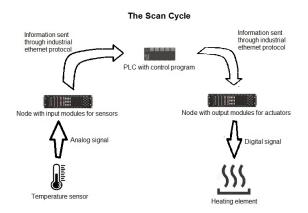

The Programmable Logic Controller (PLC) is commonly used within industrial automation to control physical processes which require precise timing. To contextualize, a PLC could be used to regulate the temperature by controlling a heating element. The process is controlled in three sequential steps. First by reading inputs, in this case from a temperature sensor, and storing the values in a data structure known as an *input image table* [10]. A user defined control program processes the input image table and sequentially executes every instruction. The corresponding output variables from the control program is stored in an *output image table* and sent to the actuator connected to the heating element. These three steps are known as the *input phase*, program phase, and *output phase*, respectively, and are together referred to as the scan cycle (see Figure 5). [10]

The scan cycle was standardized by the organization International Electrotechnical Commission (IEC), it is periodic and has a fixed periodicity [10]. The defining feature of the PLC system is the fact that it is referred to as a hard real-time system, meaning any time exceeding the scan period results in system failure known as *time cycle violation*. The scan cycle sometimes has an additional intermittent phase known as *housekeeping*, which differs between manufacturers. Housekeeping might consist of internal checks on memory, system operation, diagnostics, as well as communication requests generated between other hosts or the control program itself [10].

Figure 5: Simple flow-chart of how information travels during the scan cycle.

Returning to the heating element example, the signals sent from the temperature sensor and to the heating element can either be *analog* or *digital* [11][12]. Different *modules* are used to process and generate digital or analog *input/output* (I/O) signals. The analog or digital I/O modules are placed at *nodes* which either process received data from the PLC during the output phase, or package data collected from the modules and send them to the PLC during the input phase. The signals are usually sent through some industrial communication protocol. In the case of B&R's X20 systems used in this project, the protocol is called *Powerlink*, which is the company's proprietary protocol [11][12].

Every communication protocol operates differently. In Powerlink the communication is organized in such a way that only one node can send data at a time [11]. The communication can be synchronized according to four different specified time synchronizations; system time (internal on the PLC), X2X-link Time (for each X2X-link network), Powerlink Time (for each Powerlink network), and Time Data Points of I/O Modules [13].

The data is transferred in three periods. First an initialization frame is sent to all nodes, thereafter cyclic data is transmitted, followed by transmitting non-time critical data [11]. Up to 240 real-time devices (including the main node) can be connected in one network segment. Each node can receive and transmit 1490 bytes of process data and 1500 bytes non time-critical data per cycle with the lowest theoretical cycle-time at 100 µs. There are options available to increase the amount of

cyclic (using "Poll Request" and "Poll Response") and non time-critical data (using "Asynchronous Send") [11][12]. The data transmitted to and from the PLC is stored in the previously mentioned corresponding I/O image table which resides inside the RAM of the PLC [7].

Except data sent between nodes and the PLC, other hosts can exist in the network and send communication requests. Data can be sent either synchronously if the other host requires time critical data, or asynchronously [11]. An example of when asynchronous data is used is for devices known as *Human Machine Interfaces (HMIs)*, which provide information to personnel or operators regarding the physical process and to interact with the control system. Updating these types of devices every few milliseconds is sufficient, and therefore such data can be sent asynchronously [11][9]. Performance increments can be gained from allowing *multicast* packets to be sent if several nodes with only a small amount of process data are connected [11].

NOTE: There are events taking place during startup and shutdown. However, these events are not important for the project, the important events occur during the cyclic operation.

#### III.II The real-time operating system

To deterministically process inputs, execute the logic program, and update the corresponding outputs, PLCs employ *real-time operating systems (RTOS)*. The fundamental building block of the RTOS is the *kernel*, which generally consists of a *scheduler*, *objects*, *and services* [14]. Every event within the scan cycle can be divided into *tasks*. Tasks are schedulable objects containing sets of instructions and an assigned *priority*.

The scheduler uses algorithms to allocate CPU time to complete tasks within an established time frame [14]. In the case of the B&R system, which is based on the RTOS known as VxWorks, the algorithms used are *priority based preemptive* and *round-robin* [15]. Preemptive scheduling means that a currently running task can be preempted if there is another task with a higher priority ready. Meanwhile, round-robin allocates bursts of CPU time for every task until completion [15]. A task can be in one of three states: *running, ready,* or *blocked*. In the running state, the task has the highest priority and is currently being executed on the CPU core. In the ready state, the task is ready to run but lacks priority. In the blocked state, the task has requested access to an unavailable resource or is waiting for an event [14].

Every task is associated with a data structure called the *task-control block (TCB)* [14]. The TCB stores information regarding the specific task, including the program counter, stack pointer, other register contents, identification token, status, priority, and pointers to reserved resources as well as to the next or previous task's TCB. Whenever a task is ready which has higher priority than the one currently running, a *context switch* occurs. The context in this case is every parameter required for the CPU to execute said task. The current task's context is stored in its associated TCB, the task is released from the CPU and RAM, and the next task's context is loaded from its associated TCB and now running on the CPU. Objects are specific kernel structures, apart from tasks, there are:

- *semaphores*: allow a fixed number of tasks to enter a shared resource.

- *mutexes*: ensures only one task can access a shared resource.

- events: contains a set of *flags* to indicate specific events which a task could be waiting for.

- *mailboxes*: belong to a task and stores messages.

- queues: a buffer like FIFO data-structure to exchange data between tasks.

A combination of suitable objects are used to make up services such as inter-task communication, synchronization, or reserving resources [14]. CPU usage (%) and tasks are synonymous and to properly evaluate how much a device impacts the system a method called *task isolation* can be utilized. Tasks associated with the addition of a new type of device can be identified from logging task execution times. From the logs timing information parameters such as frequency and elapsed time can be used to pinpoint important tasks associated with the new device [16]. Measurements can now be improved if the PLC system allows user defined blockage of tasks which are non-vital for the new device.

To do a proper evaluation would also entail measuring how the CPU usage (%) responds based on the input from said device. All while capturing how concurrent tasks communicate, as well as how the RTOS scheduler preempts the tasks [16]. However, accessing all this information is sometimes not feasible in common commercial PLC systems due to information stored in TCBs being several abstraction layers away from the user. Furthermore, altering the state, priority or any other information in the task's TCB is non-advisable without proper knowledge about the system.

Within the B&R system there exists an *idle task* with the priority 0, which is the lowest priority in the entire system [17]. The idle task is scheduled whenever no user task or runtime associated task is running. A decrease in idle task time typically reflects an increase in system load. As such, measuring the change in idle task when adding a new device provides information regarding the change to the entire system. However, this also includes irrelevant activities unrelated to the new device such as updating HMIs or Ethernet communication. This is why task isolation would be recommended for higher accuracy.

Although highly prioritized and made up of many different tasks, the user defined cyclic control program does not have a specific priority within the system. For the B&R system there are something known as a task class [17]. The task class is made up of tasks with the same cycle time and priority. The user defined cyclic control program can be placed in one of eight task classes. Placing the control program in a lower task class increases the priority of every task associated with the program. As such, the control program used for increasing the CPU usage (%) is placed in the lowest task class. The allocated CPU time for idle task and cyclic control program is referred to as idle usage (%) and cyclic usage (%) respectively [17].

There are two aspects associated with the RTOS which specifically impacts the run-time performance of the PLC, namely *context switching time* and *interrupt latency* [15]. Context switching time is the summarized period of time during which the context of the currently running task is stored and the next task's context is loaded. The number of preemption's occurring during the scan cycle depends on the algorithms used by the scheduler, and relates directly to the total context switching time [15].

Interrupt latency on the other hand is the time difference between the moment an interrupt is generated, and the associated interrupt handler generates an external response [15]. The RTOS has to react quickly to external interrupt requests generated by either internal mechanisms, e.g., timers or counters, or peripherals such as I/O modules [18]. *Interrupt service routine (ISR)* is the service used by the kernel to protect the integrity of kernel data whenever an interrupt occurs, since interrupts introduce concurrency access to sensitive kernel data. The ISR uses synchronization mechanisms to protect the data. The latency is measured as the time that it takes from the arrival of an interrupt at the processor, to the start of the associated ISR. The latency varies between systems and depends on the mechanisms used, the order in which they are serviced, and the nature of the task which was interrupted [18] [14].

While the RTOS manages hardware resources and provides fundamental real-time services, the *runtime environment* serves as the abstraction layer between the control program and the RTOS [19]. Sometimes the word RTOS and runtime is used interchangeably, as in the case of the *Automation Runtime* used in B&R's system [20]. The runtime environment is usually built on top of the RTOS using *application programming interfaces (APIs)*. The runtime environment interprets the control program's instructions and interacts with the RTOS to ensure real-time execution [21].

The runtime environment also includes monitoring, which uses performance indicators such as period of tasks, maximum time frames, worst-case execution time, or response time to assess the system performance [19]. If any deviation from expected system behavior is detected, the runtime monitoring can use said performance markers to detect and mitigate the root cause [19]. There are several different ways CPUs provide monitoring tools and the Intel based B&R system uses an internal Performance Monitoring Unit (PMU) [22].

#### III.III Hardware

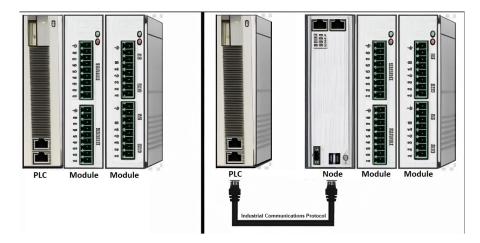

Most manufacturers design the PLC to act as a modular system. The base unit consists of essential hardware such as CPU, memory, and communication ports. The system can then be expanded with additional devices or functionalities using modules, see Figure 6. Modules can be attached to the PLC system either *serially*, using X2X-link communication, or through nodes using Powerlink. There exist numerous types of modules, this project specifically investigates modules providing additional analog or digital I/O communication.

Figure 6: Connection example: modules connected serially (left), through nodes using Powerlink (right).

There are constraints issued on the hardware used in PLC systems to increase the predictability and inherently real-time performance [23]. As such, CPU architecture is typically not multi-core since this could potentially affect the predictability of task execution. The available system memory might also be kept small to decrease access times and lower the use of extensive memory management services. Operating conditions such as temperature, humidity, vibrations, and electromagnetic radiation must be accounted for since the PLC is meant to be running for very long periods of time without interruption [23].

The modules used together with the PLC either process analog signals, measured either as a current or voltage in a certain range, or digital signals, coded as true or false. The analog modules introduce a small additional time delay to the system due to sampling and reconstruction. When comparing the analog and digital input modules used (X20AI4622 and X20DI9371), there is a small difference in the minimum allowed cycle time [24] [25].

#### **III.IV** Limitations in network capacity

As previously mentioned, there exist a default limitation of 240 nodes in the Industrial Communication Protocol provided by B&R. But it is not currently known if there exist weaknesses which lowers said limitation. Many PLC systems have two separate networks, Ethernet which is used for communication externally, and an internal network for devices, e.g., Powerlink. A good starting point to figure out any weaknesses is to see if any of the two networks share resources. This can be done by performing something known as UDP-flooding (User-Datagram-Packet-flooding) to the Ethernet network. What makes UDP-packets useful in these scenarios is the lack of "handshakes", meaning that the PLC system just tries to accept as many of the packets as possible. No concern is given to the order of the packets received. This makes it possible to "flood" the system with data which the PLC might not be able to process. If an impact on the Powerlink network can be seen when performing said flooding, then the conclusion is that the two networks are linked to the same resources.

The Powerlink network can also be subjected to injections of packets which the system is familiar with, but not necessarily expects. If the system lacks protection for filtering which packets to process on the internal network, then the possibility exists that "false" devices can be inserted into the communication. Potential weaknesses can be found by intercepting "normal" communication on the internal network, then modifying the content of each packet, and re-transmitting the modified communication. If no filtering occurs the PLC will answer each modified packet, allowing us to further evaluate the limitations on the network. However, these types of industrial communication protocols are typically very robust and the likelihood of discovering weaknesses is very slim.

Every request sent by the PLC is answered by the nodes with an Ethernet multicast frame, also known as a *Link-Layer Discovery Protocol Multicast* message, abbreviated LLDP-multicast [26]. This fact can be used to simulate other devices on the network as it essentially is a response generated by a query from the PLC. Another form of response from the nodes are *Adress Resolution Protocol* requests, abbreviated ARP request [27]. The ARP request is sent by every device on the network to discover the physical addresses of other devices. The ARP request could potentially be used to overwhelm the PLC since the PLC has to respond to the query to establish a device connection.

As previously mentioned, there are options available to increase the amount of cyclic and non time-critical data. These types of enhancements are not investigated in this work since the model should be generally applicable to any PLC system. Another topic related to the subject is network topologies. Only linear/hub topology is investigated in this work, delving into the intricacies of other topologies is outside the scope of this project.

#### III.V Program optimization

The IEC 61131–3 standard defines five programming languages, two textual, i.e., Structured Text (ST), and Instruction List (IL), as well as three graphical, i.e., Ladder Diagram (LD), Function Block Diagram (FBD), and Sequential Function Chart (SFC) [8]. The graphical languages originate from efforts to visually represent the relay logic controllers that were previously used in industrial automation. As such, the graphical languages provide a good overview of the sequential logic within the PLC system. In contrast, Structured Text (ST) more closely resembles modern high-level programming languages and provides more efficient handling of large quantities of data [8]. Only ST will be used since it provides all functionality needed to evaluate both program optimization and the impact of devices. Investigating all five languages is also unfortunately beyond the scope of this work.

There exist three types of program organization units (POUs) to structure PLC code, i.e., programs (PRGs), function blocks (FBs), and functions (FCs) [8]. The PRG manages the entire PLC and can consist of any of the other POUs, as well as unorganized code. Both PRGs and FBs possess internal memory, while FCs are executed immediately when called. As such, only FBs can be instantiated [8].

There also exist User-Defined Data Types (UDTs), which are structures of other data types [8]. The main purpose is to organize the control program by reducing the amount of code. The difference between POUs and UDTs is the fact that UDTs only represents a structure made of several components of the same or different data types, while POUs contains executable code [28]. It is important to take great care when structuring UDTs to avoid "padding-bytes", which occur to align memory addresses with the processor's memory granularity [29]. The Intel Atom used in B&R's system uses 32-bit instruction sets [30]. As such, the structure of UDTs should align with the 32-bit memory granularity to prevent padding bytes.

#### **III.VI** Developing a scalability and predictability model

Scalability is a term used to evaluate the PLC's capability to incorporate more devices into the system. Some boundaries have already been mentioned in previous sections, however, the derived model will be built on acquired test results. Predictability on the other hand represent the deterministic nature of the PLC system, i.e., the output should be the same for every repeatable input, with very small variations in execution time.

There are several factors in off-the-shelves PLC units which introduce variability into the system. For instance, general purpose processors are designed with speculative features, such as deep pipelines, out-of-order execution of instructions, unpredictable memory hierarchy, and complex replacement policies [31]. Features which heighten the functionality of the system, but lowers the predictability. Unpredictable features of the hardware also propagate onto software implementation, as it is nearly impossible for the RTOS to statically verify any timing properties [31]. Analysis techniques used to estimate system behavior might not always be valid due to unpredictable factors in the runtime, e.g., asynchronous data transfer, or runtime changeable priorities [19].

The measurements used for testing are the idle and cyclic CPU usage (%). For idle (%) usage it is specifically the assigned CPU time for a task named "idle\_task", which has the lowest priority within the system [32]. For cyclic (%) it is the time the CPU spends executing tasks related to the user defined cyclic control program, and the associated task priorities depend on the assigned priority of the cyclic program. An increase in load, such as a more complex control program or added devices, decreases the idle (%) and increases the cyclic (%) CPU usage [32].

The choice of mathematical model used for predicting the impact on performance is primarily determined by the volume of the collected samples. If larger volumes can be gathered the obvious choice for a mathematical model would be to utilize machine learning methods for predicting CPU usage (%) [33]. Unfortunately, due to the time constraint of this project the chance of being able to gather larger sample volumes is slim. Instead, the first choice is to try *linear approximation*, if the predictions match poorly, *polynomial regression* could be utilized to capture non-linear behavior. The *ridge regression* used in the method is essentially polynomial regression with the addition of a normalization factor which prevents coefficients from growing to too large values.

To fully capture the predictability of the system, there exist probabilistic models for capturing the risk of failure due to the addition of a device given the state of the system [34]. But, as with the model for scalability, the time constraint does not allow for the time consuming effort. Instead, any sudden spikes or changes to CPU usage (%) will be documented in an attempt at localizing sources for instability.

# IV Method

This chapter covers the methods used for testing the impact of nodes/modules, the limitation of the network in terms of number of supported devices, and finally program conventions which optimize the number of supported devices. As previously mentioned the system used for testing is the B&R's X20 system with all associated devices.

#### IV.I Equipment and setup

Hardware equipment, [35], [36]:

- B&R X20CP3586, PLC with Atom E680T CPU @ 1.6GHz with 512 MB DDR2 SDRAM (RAM) and 1 MB SRAM (User).

- B&R X20BB81, base module which serves as building block for a single node.

- B&R BC8083, bus controller which serves as the access point to a single node.

- B&R HB2880, network hub used to listen in on Internet traffic on the node.

- B&R AI4622, analog input module (only 4 channels are used).

- B&R AO4622, analog output module (only 4 channels are used).

- B&R DI9371, digital input module (only 4 channels are used).

- B&R DI6322, digital output module (only 4 channels are used).

- B&R PS9400, power supply.

- FLUKE 125B, mobile oscilloscope used to measure analog output signal.

Configuration:

- The system tick was synchronized to the Powerlink clock speed.

- Profiler was set to evaluate measurements using 250 000 entries.

Software [32], [37], [38]:

- B&R Automation Studio, development environment used to program the PLC.

- B&R Profiler, diagnostics tool used to measure CPU usage.

- Python 3.8.7 with Scapy, used for manipulating IP-packets.

- Wireshark 4.2.2, used to intercept IP-packets.

- Imported libraries "brsystem" and "LoopContr" into Automation Studio.

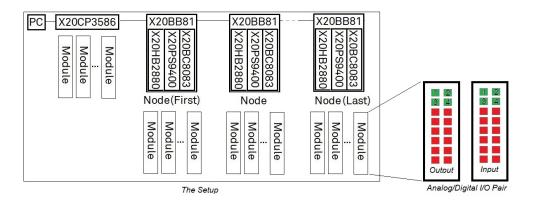

Figure 7: Example of how the B&R PLC system was set up with linear/hub-topology. Each module actually contains I/O pairs where 4 channels were cross-coupled. When modules were attached directly to the PLC (X20CP3586), they are referred to as *serially connected* using X2X-link connections. The PC is connected to the PLC through an Ethernet connection. The nodes and modules are connected to the PLC through a Powerlink connection.

#### I/O Pairs:

Every module used in the setup has been cross-coupled, see Figure 7. Each of the four channels on the input module is connected to the corresponding channels on the output module. Since analog modules only contains four channels, only four channels has been used on the digital modules as well.

#### IV.II Node and I/O testing

In this section the difference in impact on CPU usage (%) between different types of devices is established. First the difference between analog and digital signals, then a single empty node, followed by measuring combinations of nodes and modules. At the end, a verification setup is used for predicting the change in CPU usage (%) when adding a device. Instead of changing a single device in the verification setup, entire nodes with modules are changed.

#### Methodology

Each collected data sample contains three measurements. Verification of the collected sample was then done after the PLC system was made powerless for half a minute. It is important to note that the setup which was measured was first fully assembled, then disassembled device by device until only the PLC was left. The reasoning for only measuring fully assembled setups can be seen in Figure 13-14. Not only are the measurements fluctuating in Figure 14, the measurements were also inconsistent. Meanwhile, in Figure 13 the measurements were consistently increasing and decreasing for cyclic usage (%) and idle usage (%), respectively. The conclusion is that the system more quickly stabilizes itself when removing a device compared to adding. Measuring the impact of a single input module was not possible since it required an external signal source, which unfortunately could not be acquired. To solve this, every output module is connected to an input module which in turn formed I/O pairs, see Figure 7. A limit on the number of channels used in each module was set due to the analog modules only having four channels. All nodes are connected in hub/linear topology.

#### Analog vs. Digital

Determining the difference between the analog and digital modules was done by iteratively connecting one input and output module together at a time, referred to as an I/O pair, serially to the PLC using X2X-link communication. At first analog I/O pairs were evaluated using the control program (see Code Snippet 1), the test ended at a total of five I/O pairs. The measurements were repeated for digital I/O pairs after removing the analog I/O pairs.

```

//

FOR counter := -1500 TO 1500 BY 1 DO

| FOR counter := -1500 TO 1500 BY 1 DO

angle := ASIN(angle+0.01);

angle := ASIN(angle+0.01);

myString := 'string';

myString := 'string';

myInt := 5;

myInt := 5;

myConvert := INT_TO_REAL(myInt);

myConvert := INT_TO_REAL(myInt);

END_FOR

END_FOR

out1 := NOT out1;

out1 := out1+1;

out20 := out20+1;

out20 := NOT out20;

```

#### Code Snippet 1: PLC code for analog (left) and digital (right) I/O modules.

#### Empty nodes

Determining the impact of only adding empty nodes (BB81, HB2880, BC8083, PS9400) to the system using the control program in Code Snippet 2. Two samples (cyclic and idle CPU usage (%)) were gathered, first of a single empty node followed by a sample after connecting five more nodes.

```

//

1 FOR counter := -32000 TO 16000 BY 1 DO

2 angle := ASIN(angle+0.001);

3 END_FOR

```

Code Snippet 2: ST code for empty nodes program

#### Balanced cyclic vs. idle CPU usage (%)

Samples (cyclic and idle CPU usage (%)) were gathered for each node and module added to the system using the control program in Code Snippet 3. The final setup consisted of five nodes with two analog I/O pairs per node. At the end, samples were gathered after removing one module at a time until the node was empty, at which point the whole node was removed.

```

//

1 FOR counter := -32000 TO 17500 BY 1 DO

2 angle := ASIN(angle+0.001);

3 myInt := 5;

4 myString := 'string';

5 convert := INT_TO_REAL(myInt);

6 END_FOR

7 out1 := 1;

8 ...

```

Code Snippet 3: ST code for balanced cyclic vs. idle usage (%) program.

#### Unbalanced idle CPU usage (%)

Using the control program in Code Snippet 4, seven analog I/O pairs were connected to a single node. A second node was then connected, and the I/O pairs were moved to the newly added node, leaving the first node empty. A third node was then connected, and the I/O pairs were once again moved to the third node, leaving two empty nodes connected between the third node and the PLC. Once a difference in performance was noted, only one I/O module was added at a time until a "time cycle violation" occurred. Visual representation of unbalanced setup with modules placed at middle node can be seen in Figure 8.

```

//

1 FOR counter := -32000 T0 14000 BY 1 D0

2 angle := ASIN(angle+0.001);

3 END_FOR

4 out1_1 := 1;

5 out1_2 := 2;

6 ---

7 out3_7 = 14;

```

Code Snippet 4: ST code used in unbalanced setup to measure idle usage (%) for three nodes and seven analog I/O pairs per node.

Figure 8: Example of "unbalanced" setup with all modules at the  $2^{nd}$  node, while the  $1^{st}$  and  $3^{rd}$  nodes are empty.

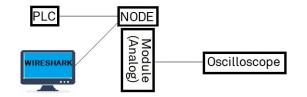

#### IV.III Network

The impact on the network when adding devices is evaluated in this section. First the stability of the network and impact on the PLC during UDP-flooding is investigated. Similarly, the performance is measured during an attempt at disrupting the Powerlink-network by injecting packets mimicking traffic when many nodes are active. Finally, the impact on signal output from an analog module is measured as both previous Powerlink-injections are performed once more. A visual representation of the test setup can be seen in Figure 9.

Figure 9: Single node PLC setup containing an analog module. An oscilloscope measures a square wave signal from the module. Network communication through the node is monitored using a PC running Wireshark.

#### **Injecting UDP-packets**

An empty node (BC8083, HB2880, PS9400) was connected to the PLC. A customized UDP-packet (see Code Snippet 5) was designed to be continuously sent, commonly referred to as flooding, to the IP-address of the PLC using its Ethernet port. No configuration was done within Automation Studio to intercept UDP-packets. A PC running Wireshark was used to monitor the communication between the node and the PLC.

```

//

import socket

import time

def send_upd(ip, port, message, a):

udp_socket = socket.socket(socket.AF_INET, socket.SDCK_DGRAM)

udp_socket.sendto(message.encode('utf-8'), (ip,port))

if a == 1:

udp_socket.shutdown(socket.SHUT_RDWR)

udp.socket.close()

__name__ == "__main__":

if

local_ip = "127.0.0.1"

target_port = 1234

maxSize = 1472

message_to_send = "A"*maxSize

try:

while(1):

send_udp(local_ip,target_port,message_to_send,0)

time.sleep(1)

except KeyboardInterrupt:

send_udp(local_ip,target_port,message_to_send,1)

Code Snippet 5: Python script using the standard "sockets" library to create UDP packets

with a specified size and destination. (Disclaimer: port and destination specified are not

```

the ones used for the test.)

#### Injecting Powerlink-packets

The setup in section *IV.III Injecting UDP-packets* was reused. However, this time Scapy was used to modify an intercepted Powerlink-packet from the hub, see Figure 9. Clones of the Powerlink-packet were generated, except for the last three address fields of the MAC-address which were set to consecutively increasing values to try and mimick additional devices on the network. The Powerlink-packets were then sent to both the Powerlink-port at the PLC, the Ethernet-port at the hub, and finally to the Powerlink-port at the empty node. Finally, two more Powerlink-packets were intercepted and left unaltered, an ARP-packet and a multicast-packet (LLDP multicast), which were also used for flooding. The Python script used can be seen in Code Snippet 6.

```

//

1 from scapy.all import *

2 pkts=rdpcap("myCapture.pcap", numberOfPkts)

3 for pkt in pkts:

4    pkt(Ether).src = new_src_mac

5    pkt(Ether).dst = new_dst_mac

6    pkt(IP).src= new_src_ip

7    pkt(IP).dst = new_dst_ip

8    del pkt(IP).chksum

9    sendp(pkt)

```

Code Snippet 6: Python script using Scapy to alter captured packets. (Disclaimer: program for intercepting Powerlink packets is not presented in the figure.)

#### Measuring output signal

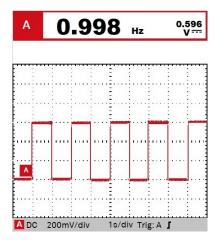

The setup in section *IV.III Injecting UDP-packets* was reused. However, an analog output module was connected to the node. The control program was modified to send out a square wave at 1 Hz using the analog output module. The amplitude and frequency were measured with an oscilloscope, then both previous PLK and UDP injections were carried out while measuring any change to the output using an oscilloscope.

#### **IV.IV** Program optimization

This section investigates two program optimizations which could improve memory allocation, CPU load and communication.

#### Memory allocation when instantiating multiples of the same datatype

The PLC was set powerless for a few minutes to ensure that any stored data was wiped from the system's registers. A clean project was created in Automation Studio and two libraries were imported into the project, first *brsystem* and finally *LoopContr*. A variable of datatype *MEMxInfo* from the *brsystem* library and a FB named *LCPID* from the *LoopContr* library was declared. A program, see Code Snippet 7, designed to only measure memory allocation once a variable *read* was forced true, was set to run at some cycle time (any cycle time works). The program first ran without any instantiated *LCPID* variable, then a single *LCPID* variable was instantiated, and finally twelve *LCPID* variables.

```

//

1 myLCPID1(enable := TRUE); (*LCPID objects were removed for the first program*)

2 ...

3 myLCPID12(enable := TRUE);

4 MEMxInfo(enalbe := read, mem_typ ;= brDRAM);

5 IF read Then

6 memVal := MEMxInfo.FreeMemSize;

7 END_IF

8 read := FALSE;

```

Code Snippet 7: Program for determining the allocated DRAM heap size for instantiating the same datatype, here *LCPID*, multiple times. First a program for how much memory is allocated at the start was used, without *myLCPID* objects. Then a program for a single *LCPID* object. Finally for instantiating up to twelve *LCPID* objects.

#### Verifying padding bytes

The PLC was set powerless for a few minutes to ensure that any stored data was erased from the system's registers. A clean project was created in Automation Studio and an empty IEC library was added. An UDT was defined in the empty library with the following structure of data types; UDINT, BOOL, BOOL, BOOL, BOOL, in that specific order. A variable of the UDT was declared and a program was created running at some cycle time. The variable of the UDT was instantiated in the program and the IEC standard function SIZEOF() was used to measure the allocated memory of the UDT. The structure of the UDT was then changed to the specific structure; BOOL, UDINT, BOOL, BOOL, BOOL. Once again the allocated memory was measured using SIZEOF(). The two structures can be seen in Code Snippet 8.

```

//

1 myBadDatatype: -> Controlled using SIZEOF(myBadDatatype);

2 BOOL

3 UDINT

4 BOOL

5 BOOL

6 myGoodDatatype: -> Controlled using SIZEOF(myGoodDatatype);

9 UDINT

9 BOOL

10 BOOL

11 BOOL

12 Coll Coll is to Cit to Cit

```

Code Snippet 8: Structure of the UDTs with the command to verify the allocated memory using SIZEOF() function.

#### Impact of padding bytes on performance

Continuing from the previous subsection *IV.IV verifying padding bytes.* A hierarchy data structure was created using first the "bad" UDT structure and finally the "good" UDT structure, see Figure 10 (left). A new program was created in which a for-loop read and write within the hierarchy, see Figure 10 (right). The difference in idle and cyclic CPU usage (%) was measured using the "bad" and "good" data structures.

```

unter := -15000 TO 15000 BY 1 DO

counter := -15000 T0 15000 BY 1 D0

my8Struct.var8_1.var7_1.var6_1.var5_1.var4_1.var3_1.var2_1.var1_1.my8adDatatype.BOOL1 := NOT my8Struct.var8_6.var7_6.var6_6.var5_6.var4_6.var3_6.var2_6.var1_6.my8adDatatype.BOOL1

my8Struct.var8_1.var7_2.var6_2.var4_2.var3_2.var2_2.var1_2.my8adDatatype.UDINT := my8Struct.var8_5.var7_5.var6_5.var4_5.var3_5.var2_5.var4_5.var3_5.var2_5.var4_5.var3_5.var2_5.var4_5.var3_5.var2_5.var4_2.var1_2.my8adDatatype.BOOL1 := NOT my8Struct.var8_4.var7_4.var6_4.var5_4.var4_4.var3_4.var2_4.var1_5.my8adDatatype.BOOL2 := NOT my8Struct.var8_4.var7_4.var6_4.var5_4.var4_4.var3_4.var2_4.var1_4.my8adDatatype.BOOL3 := NOT my8Struct.var8_5.var7_3.var6_3.var6_3.var6_3.var4_3.var2_3.var1_3.my8adDatatype.BOOL3 := NOT my8Struct.var8_4.var7_4.var6_4.var5_4.var4_4.var2_4.var2_4.var1_4.my8adDatatype.BOOL3 := NOT my8Struct.var8_5.var7_2.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var6_3.var

myBadDatatyp

myBadDatatype

my8Struct.var8 9.var7 9.var6 9.var5 9.var4 9.var3 9.var2 9.var1 9.my8adDatatype.BOOL1 := NOT my8Struct.var8 4.var7 4.var5 4.var4 4.var3 4.var2 4.var1 4.my8adDatatype.BOOL1

my8Struct.var8 8.var7 8.var5 8.var4 8.var5 8.var4 8.var3 8.var2 8.var1 8.my8adDatatype.UDINT := my8Struct.var8 5.var5 5.var5 5.var4 5.var5 5.var4 5.var2 5.var1 5.my8adDatatype.BODL3

my8Struct.var8 7.var7 7.var6 7.var5 7.var4 7.var3 7.var2 7.var1 7.my8adDatatype.BODL3 := NOT my8Struct.var8 6.var5 6.var5 6.var4 6.var5 6.var4 6.var5 6.var4 6.var5 6.var4 6.var5 6.var4 5.var2 6.var1 6.my8adDatatype.BODL3

my8Struct.var8 6.var7 6.var6 6.var5 6.var4 6.var3 6.var2 6.var1 6.my8adDatatype.BODL3 := NOT my8Struct.var8 7.var7 7.var6 7.var5 7.var4 7.var3 7.var2 7.var1 7.my8adDatatype.BODL3

my8Struct.var8 5.var7 5.var4 5.var4 5.var3 5.var2 5.var1 6.my8adDatatype.BODL4 := NOT my8Struct.var8 7.var7 7.var6 7.var5 7.var4 7.var3 7.var2 7.var1 7.my8adDatatype.BODL4

my8Struct.var8 5.var7 5.var4 5.var4 5.var3 5.var2 5.var1 6.my8adDatatype.BODL5 := NOT my8Struct.var8 7.var7 7.var6 7.var5 7.var4 7.var3 7.var2 7.var1 7.my8adDatatype.BODL4

my8Struct.var8 5.var7 5.var4 5.var4 5.var3 5.var2 5.var1 6.my8adDatatype.BODL5 := NOT my8Struct.var8 8.var7 8.var6 9.var5 5.var4 9.var3 9.var2 9.var1 9.my8adDatatype.BODL5

my8Struct.var8 4.var7 5.var4 4.var5 5.var4 5.var3 5.var2 5.var1 4.my8adDatatype.BODL5 := NOT my8Struct.var8 9.var7 9.var6 9.var5 9.var4 9.var3 9.var2 9.var1 9.my8adDatatype.BODL5

my8Struct.var8 5.var7 5.var4 5.var3 5.var1 4.my8adDatatype.BODL5 := NOT my8Struct.var8 9.var7 9.var6 9.var5 9.var4 9.var3 9.var2 9.var1 9.my8adDatatype.BODL5

my8Struct.var8 5.var5 5.var4 5.var3 5.var1 9.my8adDatatype.BODL5 := NOT my8Struct.var8 9.var7 9.var6 9.var5 9.var4 9.var3 9.var2 9.var1 9.my8adDatatype.BODL5

my8Struct.var8 5.var4 5.var5 5.var4 5.var3 5.var1 9.my8adDatatype.BODL5 := NOT my8Struct.var8 9.var7 9.var6 9.var5 9.var4 9.var3 9.var2 9.var1 9.my8adDatatype.BODL5 0.var5 9.var5 9.var4 9

my1Struct

P. UDTNT+1

→ var2_9

my1Struct

7Struc

var7

my6Struct

...

↓ var7_9

w8Struct

↓ var8_1

my6Struct

my8Struct.var8 1.var7 7.var6 4.var5 1.var4 7.var3 4.var2 1.var1 7.myBadDatatype.BOOL1 := NOT my8Struct.var8 9.var7 3.var6 6.var5 9.var4 3.var3 6.var2 9.var1 3.myBadDatatype.BOOL1

mySStruct.varg_1.varg_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.vars_1.v

my7Struct

....

→ var8_9

my7Struct

```

Figure 10: Hierarchy data structure, here with the "bad" data structure which was later replaced with the "good".

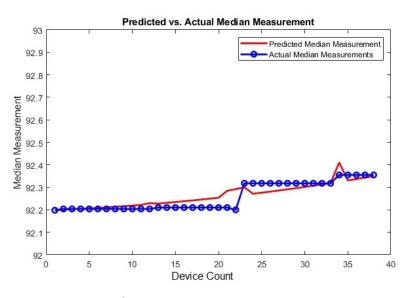

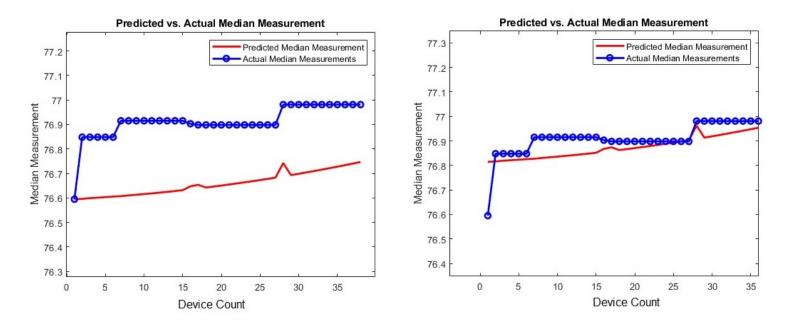

#### Model verification

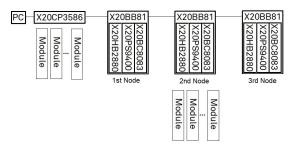

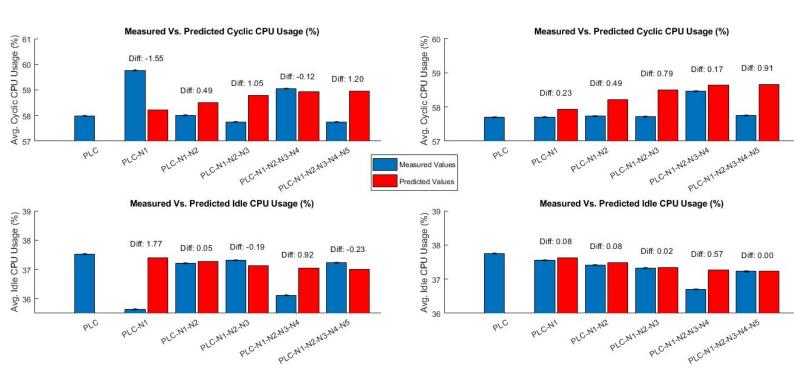

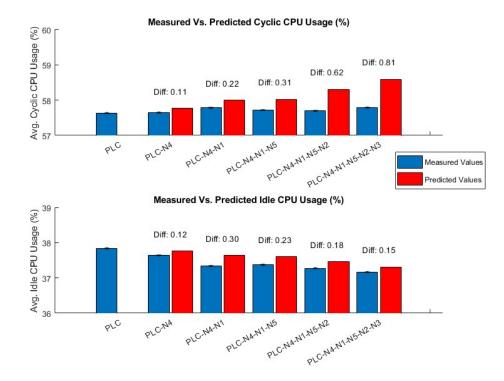

The measurements from section IV.II Node & I/O Testing are used to establish the best relationship between the number of connected devices. A linear relationship is tested using the setup in Table 1. The nodes are, as for every previous setup, connected in hub/linear topology.

| Node: | Modules:                                                              |  |  |

|-------|-----------------------------------------------------------------------|--|--|

| N1    | AO4622 AI4622 DI9371 DO6322 AO4622 AI4622 DO6322 DI9371               |  |  |

| N2    | DI9371 DO6322 AI4622 AO4622 AI4622 AO4622 DI9371 DO6322 AI4622 AO4622 |  |  |

| N3    | AI4622 AO4622 AI4622 AO4622 AI4622 AO4622 DI9371 DO6322 DI9371 DO6322 |  |  |

| N4    | AO4622 AI4622 AO4622 AI4622                                           |  |  |

| N5    | Empty                                                                 |  |  |

Table 1: The modules connected to each node in their respective order.

## V Results

The following section contains the results from the tests carried out based on chapter *IV Method*. The variability for each measurement is displayed as the standard deviation. Normally, using averages and standard deviation for measurements not following the *normal distribution* should be avoided. However, due to the small sample sizes it is difficult be entirely certain of which distribution the measurements follow. Goodness-of-fit and probability plots (Q-Q plots) provided by 'fitdist' function in Matlab were used to identify the following distributions:

- Measurements in *IV.II Balanced cyclic vs. idle usage (%)* does not follow the normal distribution, idle usage (%) distinctly follows the *general pareto distribution*, while cyclic usage (%) follows the *kernel distribution*.

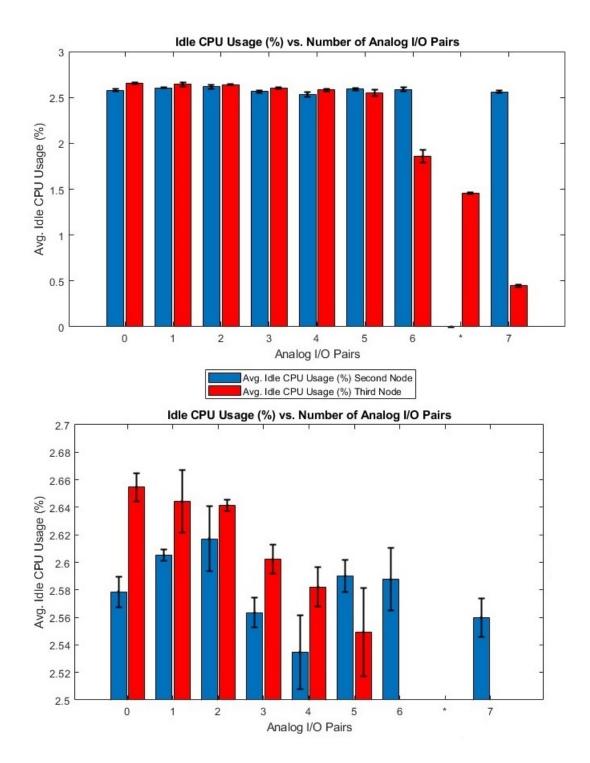

- Measurements in *IV.II Unbalanced idle usage* (%) the  $2^{nd}$  node (blue bars) adheres to a normal distribution, and  $3^{rd}$  node (red bars) approximates the general pareto distribution.

Due to earlier remarks regarding the small sample sizes, the choice was to still use averages and standard deviation. However, the identified distributions are still mentioned as not to disclose any information from the reader.

#### V.I Node and I/O testing

This section covers results regarding the evaluation of impact on performance from the addition of a device.

#### Analog vs. digital

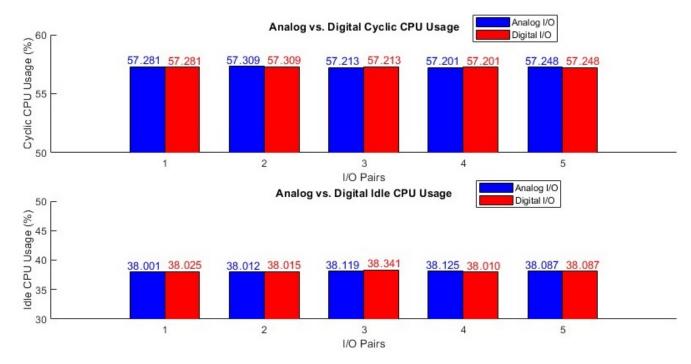

No discernible differences were found between analog and digital modules when connected serially using X2X-link communication to the PLC, see Figure 11

Figure 11: Comparison between analog (blue) and digital (red) modules. Each input module is cross coupled to an output module, referred to as an I/O pair. All modules were attached serially to the PLC using X2X-link communication.

#### Empty nodes

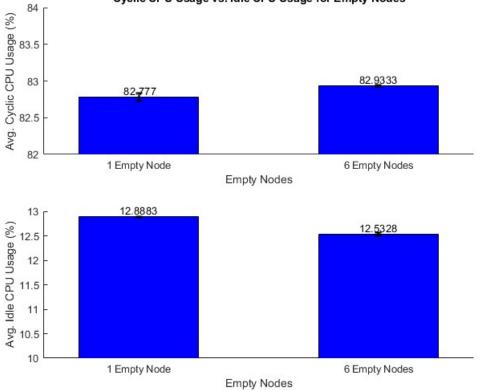

The differences (cyclic and idle usage (%)) between a single empty node and six nodes in hub/linear topology can be seen in Figure 12. Calculated averages can be seen in Table 2. As expected, the cyclic load (%) increases while the idle load (%) decreases. The change in idle load (%) appears to be more significant compared to cyclic load (%) when adding an empty node.

Cyclic CPU Usage vs. Idle CPU Usage for Empty Nodes

Figure 12: Cyclic and idle CPU usage (%) measurements for one and six empty nodes.

| Avg. cyclic CPU usage (%) per node | 0.0313  |

|------------------------------------|---------|

| Avg. idle CPU usage (%) per node   | -0.0711 |

Table 2: Average CPU usage (%) for adding one empty node. Negative values for idle (%) usage due to the decreased idle CPU usage (%) when adding a device.

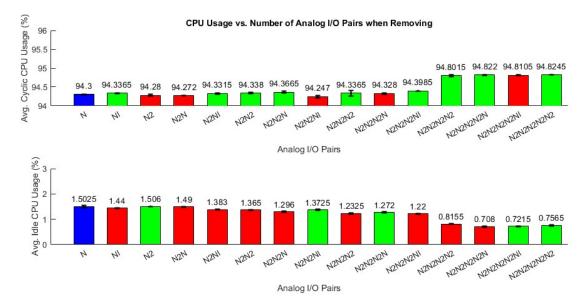

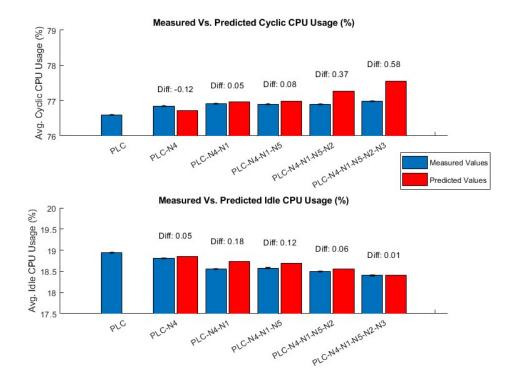

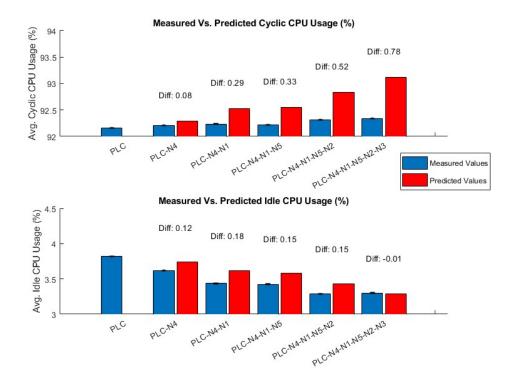

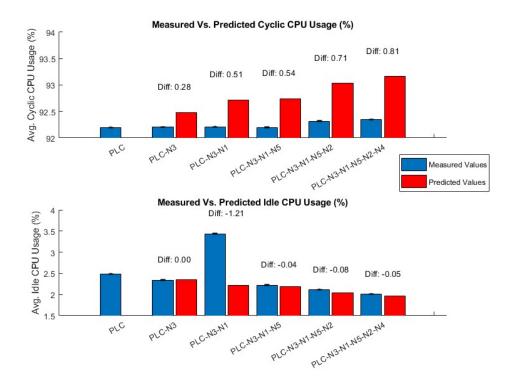

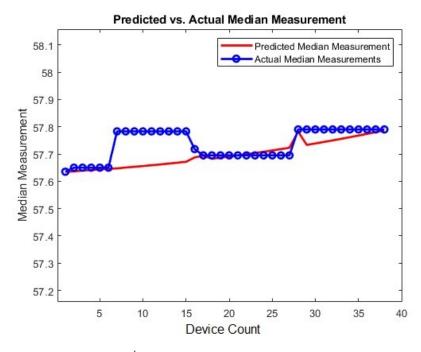

#### Balanced cyclic Vs. idle CPU usage when removing devices

The measurements (cyclic and idle (%) usage) gathered after removing a device from the "balanced" setup can be seen in Figure 13, and Table 3. Only the differences (cyclic and idle usage (%)) for the addition of a node can be seen in Table 4. As expected, the cyclic load (%) increases while the idle load (%) decreases. Some measurement irregularities such as increased load when measuring idle load (%) and vice versa, as well as a sudden spike in load at the fourth node. The gathered results can be used for developing models predicting the impact on CPU load from both modules as well as nodes.

Figure 13: Cyclic and idle usage (%) for consecutively removing devices from preexisting setup consisting of five nodes with two analog I/O pairs per node. The "N" symbol represents a node, the "I" symbol represents one I/O pair and "2" represents two I/O pairs. Color change represents even (blue), increase (green), and decrease (red) in (%) compared to previous bar.

| Node/Pair:     | Diff. idle $(\%)$ : | Diff. cyclic $(\%)$ : |

|----------------|---------------------|-----------------------|

| 1/1            | 0.0625              | 0.0365                |

| 1/2            | 0.066               | -0.0565               |

| 2/1            | -0.1230             | 0.0515                |

| 2/2            | -0.0180             | 0.0065                |

| 3/1            | 0.0075              | -0.0910               |

| 3/2            | -0.140              | 0.0895                |

| 4/1            | -0.0125             | 0.0620                |

| 4/2            | -0.4045             | 0.4030                |

| 5/1            | -0.0940             | 0.0090                |

| 5/2            | 0.0350              | 0.0140                |

| Avg. Diff (%): | -0.0746             | 0.0525                |

Table 3: Differences between average (%) idle and cyclic usage (%) for I/O modules (excluding impact of nodes). Negative values due to the decreased idle usage (%) when adding a device. However, cyclic usage (%) values should stay positive.

| Node/Pair:     | Diff. idle $(\%)$ : | Diff. cyclic $(\%)$ : |

|----------------|---------------------|-----------------------|

| 2/0            | -0.0160             | -0.0080               |

| 3/0            | -0.0690             | 0.0285                |

| 4/0            | -0.0395             | -0.0081               |

| 5/0            | -0.1075             | 0.0205                |

| Avg. Diff (%): | -0.0383             | 0.008225              |

Table 4: Impact of adding an empty node to the setup. The measured difference (%) is between the previous full node and the newly added empty node, i.e., 2/0 representing the measured difference between the first full node 1/2 and the new empty node 2/0.

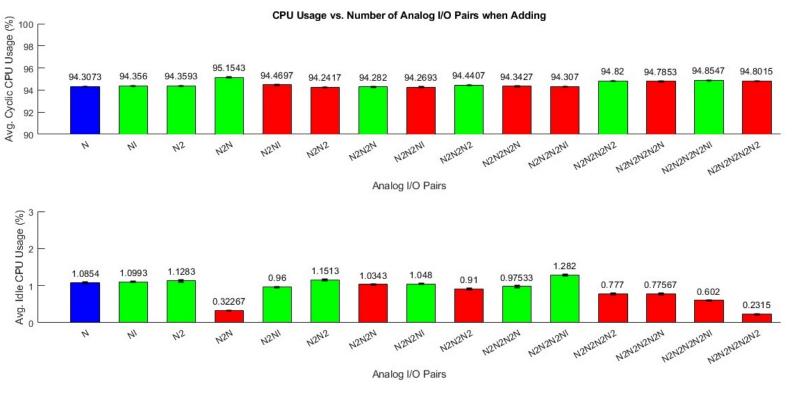

#### Balanced cyclic vs. idle CPU usage when adding devices

One single instance of measurements (cyclic and idle usage (%)) gathered when measuring after adding a device to a setup. This serves as an example on what the measurements looks like if the system has not stabilized between measurements. While the measurements of cyclic load (%)increases and idle load (%) decreases, it is impossible to distinguish how large of an impact each individual node and module have on the system.

Figure 14: Non-stabilized setup, same as seen in Figure 13, but instead of removing devices measurements were taken for each **added** device. Same color scheme as Figure 13, where blue represents no change, green represents an increase, and red represents a decrease in CPU load (%) compared to previous measurement.

#### Unbalanced idle CPU usage (%)

Results from the unbalanced setup as seen in Figure 8. The measurements (see Figure 15) appears to almost reach stagnation up until the sixth module pair where a sudden change can be seen for the third node (red bars). However, upon a closer look at the bottom graph shows an interesting observation. Here it appears as if the measurements for the second node fluctuates, while the measurements for the third node steadily decreases. Suggesting that the system might be more heavily strained when the load was placed at the third node.

Average change to idle usage (%) is calculated in Table 5. Meanwhile an additional single module (denoted \*) was added at the sixth I/O pair and the following measurements are presented in Table 6. The different behaviors when placing a load at the second node (blue bars) compared to the third node (red bars) further suggests that the system reacts differently to balanced/unbalanced configurations. The results also suggests that more data should be acquired in regards to how nodes behaves to acquire an improved and more accurate model.

Figure 15: Idle CPU usage (%) for seven analog I/O pairs attached to an unbalanced setup. The graph below is a close up of the graph above. Blue bars represent two nodes with the first node being empty, and the second node having seven I/O pairs. Red bars represent the addition of a third node with the two first being empty, and the third node having seven I/O pairs. The "\*" symbol is representing only a single analog I/O module added. Measurements from the first node are omitted due to insignificant difference to the second node.

| Node/Pair:     | Diff. idle $(\%)$ : | Node/Pair:     | Diff. idle $(\%)$ : |

|----------------|---------------------|----------------|---------------------|

| 2/1            | 0.0266              | 3/1            | -0.0102             |

| 2/2            | 0.0120              | 3/2            | -0.0030             |

| 2/3            | -0.0538             | 3/3            | -0.0392             |

| 2/4            | -0.0286             | 3/4            | -0.0200             |

| 2/5            | 0.0554              | 3/5            | -0.0328             |

| 2/6            | -0.0026             | -              | -                   |

| Avg. Diff (%): | 0.0015              | Avg. Diff (%): | -0.0210             |

Table 5: Change in idle usage (%) for unbalanced setup with two and three nodes. The left side of the table represents two nodes, with the first node empty and increasing number of attached analog I/O pairs. The right side of the table represents three nodes with the two first being empty and an increasing number of attached analog I/O pairs.

| Node/Pair:         | Diff. idle $(\%)$ : |

|--------------------|---------------------|

| 3/6                | -0.6916             |

| 3/*                | -0.4012             |

| 3/7                | -1.0080             |

| Avg. Diff idle (%) | -0.7003             |

Table 6: Differences in idle CPU usage (%) between I/O pairs for the third node. The "\*" symbol represent the addition of a single analog input module to the  $6^{th}$  I/O pair on the third node. Negative values for idle usage (%), due to the decreased usage (%) when adding a device.

#### V.II Network

This section covers results related to the network analysis.

#### **Injecting UDP-packets**

No discernible disturbances were found using Wireshark. The altered UDP-packets used for flooding did not affect neither cyclic nor idle usage (%).

#### Injecting PLK-packets

No discernible disturbances were found using Wireshark. Neither the altered PLK-packets, nor the unaltered ARP-packets and unaltered multicast-packets affected the cyclic or idle usage (%).

#### Measuring output signal

The measured output signal (seen in Figure 16) using the oscilloscope had the same amplitude and frequency before and after the injected UDP and PLK-packets.

Figure 16: Oscilloscope reading for all measured signals, no difference was noted between any of them.

#### V.III Program optimization

This section covers results regarding the program optimization.

#### Memory allocation for FBs

The three programs were executed at three different points after the system had been disconnected for a few minutes and using clean projects. From Table 7 the average amount of allocated memory (bytes) per instantiated variable can be calculated using measurements A, B, and C. The average difference in allocated memory between the first and second instantiation of the FB (in the code LCPID) was 122 bytes, with a standard deviation of 0.8 bytes. After instantiating twelve of the same FB the average allocated memory dropped to 51 bytes, with a standard deviation of 1.2 bytes. The average amount of allocated memory for a single variable lowers from 1470 bytes down to roughly 51 bytes when 12 variables of the same FB is instantiated.

| No. of instantiated FBs: | Measurement A (bytes): | Measurement B (bytes): | Measurement C (bytes): | Avg./Avg. Diff. (bytes): |

|--------------------------|------------------------|------------------------|------------------------|--------------------------|

| No variable              | -                      | -                      | -                      | -                        |

| 1 variable of same FB    | -1 464                 | -1 468                 | -1 478                 | -1470 / 0                |

| 2 variables of same FB   | -1 584                 | -1 590                 | -1 602                 | -1592 / -122             |

| 12 variables of same FB  | -2 094                 | -2 090                 | -2 112                 | -2098.667/ -50.667       |

Table 7: DRAM heap memory allocation after instantiating new variables of the same FB. Average differences (Avg. Diff) calculated by subtracting the measured average and dividing by the number of variables. As an example, the average difference of 12 variables is  $\sum (A + B + C)/3 = 2098.667$  bytes, subtracting the average for 2 variables (1592 bytes) gives us 506.667 bytes, and finally dividing by the difference in variables (12-2) results in 50.6 bytes.

#### Verifying padding bytes

The two structures "myBadDatatype" and "myGoodDatatype" presented in Table.8 shows that there are indeed inserted padded bytes for "myBadDatatype" structure.

| UDTs:          | Datatype1: | Datatype 2: | Datatype 3: | Datatype 4: | Datatype 5: | SIZEOF() value (bytes) |

|----------------|------------|-------------|-------------|-------------|-------------|------------------------|

| myBadDatatype  | BOOL       | UDINT       | BOOL        | BOOL        | BOOL        | 12                     |